Leiterplattendesign für Kommunikationsprodukte

Wir entwickeln

Hochkomplexe Layouts für hochkomplexe Ansprüche

Unsere Langjährige Erfahrung im Bereich Leiterplattendesign und -Layout macht es uns möglich Ihnen beste Qualität und Funktionalität vor allem für hochkomplexe Layouts zu bieten. Multilayer, Microvias, High-Density-Leiterplatten, Backplanes, der Einsatz von BGAs mit mehr als 1000 Pins, impedanzkontrolliertes und EMV-gerechtes Design sind mehr als nur “vertraute Materie” für unser Team.

Dabei kümmern wir uns um den gesamten Design-Prozess von der Erstellung von Stromlaufplänen und Stücklisten über den Entwurf bis zur Datenaufbereitung für die Herstellung und Baugruppenfertigung.

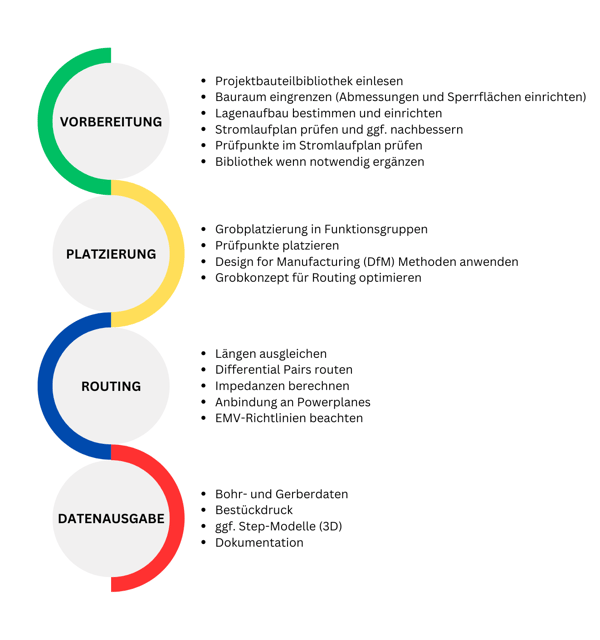

Unser Entwicklungszyklus

Leistungsumfang

Am Ende unserer Projektarbeit erhalten Sie:

Know-how

Unsere Teammitglieder verfügen über eine Reihe von Fachkenntnissen zur Erstellung komplexer und anspruchsvoller Designs:

-

High-Density Interconnect (HDI)/Microvia Design: Fachkenntnisse in der Gestaltung von Leiterplatten mit Mikrovias, die häufig in Ball Grid Array (BGA)- und Mikro-BGA-Gehäusen verwendet werden.

-

Flex/Rigid-Flex-Entwurf: Erfahrung im Design von flexiblen und starr-flexiblen Leiterplatten.

-

EMV-gerechter Entwurf: Kenntnisse im Design von Leiterplatten zur Minimierung elektromagnetischer Störungen und zur Gewährleistung der elektromagnetischen Verträglichkeit.

-

Impedanzgesteuertes Hochgeschwindigkeits-Design: Erfahrung im Design von Leiterplatten für Hochgeschwindigkeitssignale, Impedanzkontrolle für Signalintegrität in Technologien wie DDR3, DDR4, PCI Express und 10 GB.

-

Analog-Entwurf: Fertigkeiten im Design von PCBs für analoge Schaltungen.

-

Thermisches Management: Kenntnisse über die Kühlung von PCBs mit Aluminiumkernen und anderen Methoden.

-

Entwurf für Fertigung/Testbarkeit (DFM/DFT): Erstellung von Layouts, die für eine effiziente Fertigung und Prüfung optimiert sind.

-

Simulation und Modellierung: Fähigkeit, realistische Modelle von Baugruppen zu erstellen und ihr Verhalten zu simulieren, um Entwurfsiterationen zu reduzieren.

Profitieren sie von unserer Expertise

-

spezialisiertes Fachwissen

- Erfahrungen mit komplexen Multilayer-Leiterplatten, High-Density Interconnect (HDI), Microvias, BGAs, Flex-/Rigid-Flex-Designs und Hochgeschwindigkeitsdesigns

-

Aktuelle Technologie und Werkzuege

- Wir verwenden state-of-the-art Tools und Technologien für Design und Simulation der Leiterplatten.

-

Zeit- und Kostenersparnis

- Expertise und langjährige Erfahrung ermöglichen einen kurzen Bearbeitungszeitraum und spart letztendlich Kosten

-

Umfassende Unterstützung

- Wir begleiten den gesamten Designprozess, von der Erstellung von Schaltplänen bis zur Vorbereitung von Fertigungsdaten.

-

hohe Qualität und Zuverlässigkeit

- Durch unsere Partnerschaft mit qualifizierten Herstellern gewährleisten wir eine hohe PCB- und Montagequalität.

-

Problemlösung

- Wir verstehen Produktentwicklung als die Generierung von Erkenntnissen. Nennen wir sie nicht Probleme!

Entwicklungswerkzeuge

Design Tools

Simulations Tools

CAD Tools

Wir sind Mitglied im Fachverband Elektronikdesign und -fertigung e.V. (FED) für:

- Branchen-Networking

- Austausch mit Fachexperten

- Nutzen des Schulungsangebot

- Zugang zu Arbeitskreisen und Projektgruppen

- Diskussion und Weiterbildung in der Regionalgruppe Dresden